- 您现在的位置:买卖IC网 > Sheet目录1991 > CS5346-CQZR (Cirrus Logic Inc)IC ADC AUD 103DB 200KHZ 48-LQFP

DS861PP3

29

CS5346

7.3

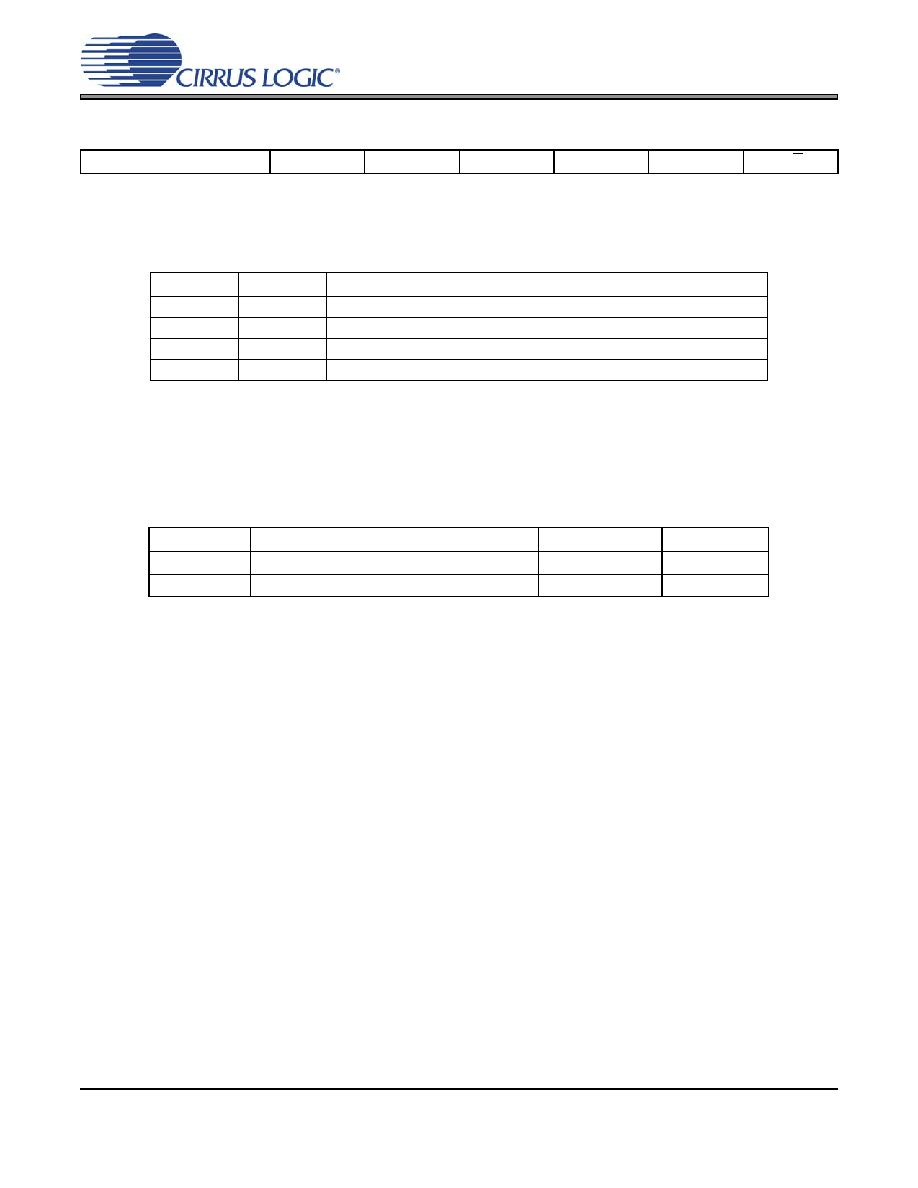

ADC Control - Address 04h

7.3.1

Functional Mode (Bits 7:6)

Function:

Selects the required range of sample rates.

7.3.2

Digital Interface Format (Bit 4)

Function:

The required relationship between LRCK, SCLK and SDOUT is defined by the Digital Interface Format

7.3.3

Mute (Bit 2)

Function:

When this bit is set, the serial audio output of the both channels is muted.

7.3.4

High-Pass Filter Freeze (Bit 1)

Function:

When this bit is set, the internal high-pass filter is disabled. The current DC offset value will be frozen and

continue to be subtracted from the conversion result. See “High-Pass Filter and DCOffset Calibration” on

7.3.5

Master / Slave Mode (Bit 0)

Function:

This bit selects either master or slave operation for the serial audio port. Setting this bit selects Master

Mode, while clearing this bit selects Slave Mode.

7

65

432

10

FM1

FM0

Reserved

DIF

Reserved

Mute

HPFFreeze

M/S

FM1

FM0

Mode

0

Single-Speed Mode: 8 to 50 kHz sample rates

0

1

Double-Speed Mode: 50 to 100 kHz sample rates

1

0

Quad-Speed Mode: 100 to 200 kHz sample rates

11

Reserved

Table 6. Functional Mode Selection

DIF

Description

Format

Figure

0

Left-Justified (default)

0

1IS

1

Table 7. Digital Interface Formats

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CS5351-BZZ

IC ADC AUD 108DB 204KHZ 24-TSSOP

CS5361-DZZ

IC ADC AUD 114DB 204KHZ 24-TSSOP

CS5364-CQZR

IC ADC 4CH 114DB 216KHZ 48-LQFP

CS5366-DQZR

IC ADC 6CH 114DB 216KHZ 48-LQFP

CS5368-DQZ

IC ADC 8CH 114DB 216KHZ 48-LQFP

CS5381-KSZ

IC ADC AUD 120DB 192KHZ 24-SOIC

CS53L21-CNZR

IC ADC STEREO 24BIT 98DB 32-QFN

CS5509-ASZR

IC ADC 16BIT SGL SUPP 16-SOIC

相关代理商/技术参数

CS5346-DQZ

功能描述:模数转换器 - ADC 103dB 24Bit 192kHz Stereo Audio ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

CS5346-DQZR

功能描述:音频数/模转换器 IC 103dB 24Bit 192kHz Stereo Audio ADC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

CS5349-000

制造商:TE Connectivity 功能描述:4110-10-340812

CS5349-BP

制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 16-Bit

CS5349-BS

制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 16-Bit

CS5349-KP

制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 16-Bit

CS5349-KS

制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 16-Bit

CS5351

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:108 dB, 192 kHz, Multi-Bit Audio A/D Converter